��֥�ٻ��63�����ڼ������

ͨ���������ڴ洢��Ԫ���ЧӦ��ʵ�ֶ�λ/��Ԫ(multi-bit/cell) NAND������ܶ���ƹ����ͻ���Խ�չ

����--(������ҵ��Ѷ)--��֥��˾(TOKYO:6502)�ٻ��63�����ڼ�������ý������ձ���ҵ���������ʢ���Ľ������Ͽ��˶�֥�����ڼ�˰뵼�弼��������ȡ�õijɼ���

����ڽ�(Okochi Prize)ʼ��1954�ּ꣬�ڱ��ð������������з����ڵ��������Ĺ�ҵ���̽�����������꣬ƾ����Խ�з������췽���ͻ���ɾͣ���֥����ٻ�ý�����꣬�ý�������˶�֥ͨ���������ڴ洢��Ԫ���ЧӦʵ�ֶ�λ/��ԪNAND������ܶ���ƹ����ͻ���Լ������佱������3��24���ڶ������С�

��֥������NAND������һ��洢��������ʹ�ִ�����ز����ٵĸ��������豸��Ϊ���ܡ�NAND����㷺Ӧ���������ֻ���ƽ����Ժ��˵��ԡ�SD�洢����USB�洢���Լ�SSD�ȹ�ҵ�洢�豸��

������ƹ��������Ͷ�λ/��Ԫ������NAND������ʵ�ֵͳɱ���ͬʱ�߱���洢������Ȼ��������С�ͻ�ʹ�洢��Ԫ��Ϊ���գ���ˣ��������ڵ�Ԫ���б��ʱ���洢��Ԫ�еĵ����������ܵ�Ӱ�졣�����ø��ٵ�������¼���ݵĶ�λ�洢��Ԫ��˵������һ���������⣬�ᵼ�����ݶ�ȡ����

��֥�������ɹ�Ӧ����MLC (2bit/cell) NAND���棬��ȷ����ˮƽ�����ݿɿ��ԡ��ü����ԶԪ��̴���Ϊ������������һ����Ԫ�н���һλ��̣�Ȼ�������ڵ�Ԫ�н���һλ��̣�����ڵ�һ��Ԫ�н�����һλ�ı�̡����ֵ�����������λ�ķ�������Ч�������ڵ�Ԫ֮�����ϸ��š��ô��������ǵ�Ԫȷ����Ԫ�б�̵�λ�����������в�Ʒ���ݡ�

һ����Ƚ��ļ���֧�ֶ�֥����߿ɿ���TLC (3bit/cell) NAND�������ͨ��ÿ��Ԫλ�����ߵ�������̷�ʽ������������TLC NAND��Ԫ����ȷ�����١�ȷ�ı�̣��������������ڵ�Ԫ֮�����ϸ��š�

���ö�λ/��Ԫ������СоƬ�ߴ�ɴ��������洦�����������ڼ��ܺģ����ټӹ��ڼ�������������ͻ���Ӱ�죻�Լ���߲���������֧�ֶ�֥�����������ͳɱ���NAND���������г���Ϊ���㷺�IJ�ƷӦ�úͲ��Ͻ�������Ϣ������ṩ֧�֡�

��֥�������ƶ����漼�����£���������Ϣ����ҵ����

����

ͨ���������ڴ洢��Ԫ���ЧӦʵ�ֶ�λ/��ԪNAND����ĸ��ܶ���ƹ���ļ���

������

Noboru Shibata���ڴ沿

Masaki Fujiu���ڴ沿

Hiroshi Sukegawa���뵼���з�����

��֥��˾�洢�����Ԫ�������������˾

���ڶ�֥

��֥��1875���ڶ�����������֥��˾��һ�ҡ��Ƹ���ȫ��500ǿ��˾��������������Դ��������ʩ�ʹ洢����Ĵ��¼���Ϊ�ͻ���������õ���������硣�ڡ�Ϊ������͵�������족�ľ�Ӫ����ָ���£���֥ƾ��鼰ȫ���Ա��������188,000�˵�551�Ҹ�����˾�����ƶ�ҵ��չ��ʵ�ֳ���5.6������Ԫ�������۶Լ��500����Ԫ��2016��3��31�գ���

������Ϣ����ʶ�֥��վ��www.toshiba.co.jp/index.htm

�����������ӣ�http://www.iruis.com/News/cninfo/43628.shtml

������Ѷ

��Ψ�㷨�ۡ��Ľ���ͷ������ȥ�δӣ�

�����222

���������ѵ�ʱ���Ѿ���ȥ��С���Ѿ���������

�����141

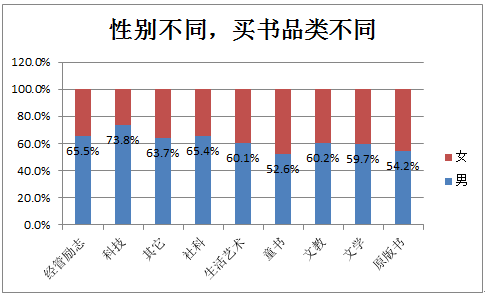

����ͼ�鷢��2016��ͼ�������г���ȱ���

�����140

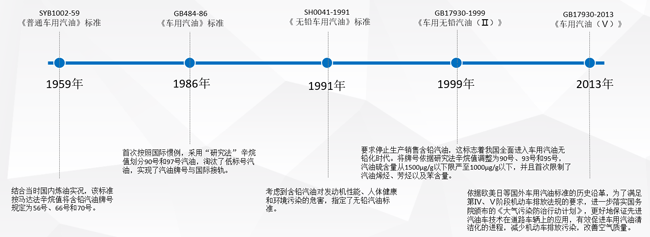

ͼ�ɷ����й�ȼ��Ʒ�����ݷֲ�����

�����132

�������ڲ���֧������Ұ������

�����107

ȥ�����Ͷ�߽���Ϊ��ͬ����

�����102

�Ŷ����� ��ҵ��˾Ӧ��ѡ����ְ칫��ʽ��

�����102

�ٶȾޱ䣺½�����ˣ�������Ҳ����

�����55

��������˫�н���4����Ԫ����3��ŷ���������°桭

�����48

�й�����ȫ��������������ƽ̨����

�����32